345 字

2 分钟

【计组】第四章整理(Part 1)

参考:@JA101617 静安的计组笔记 && 咸鱼暄的计组笔记.

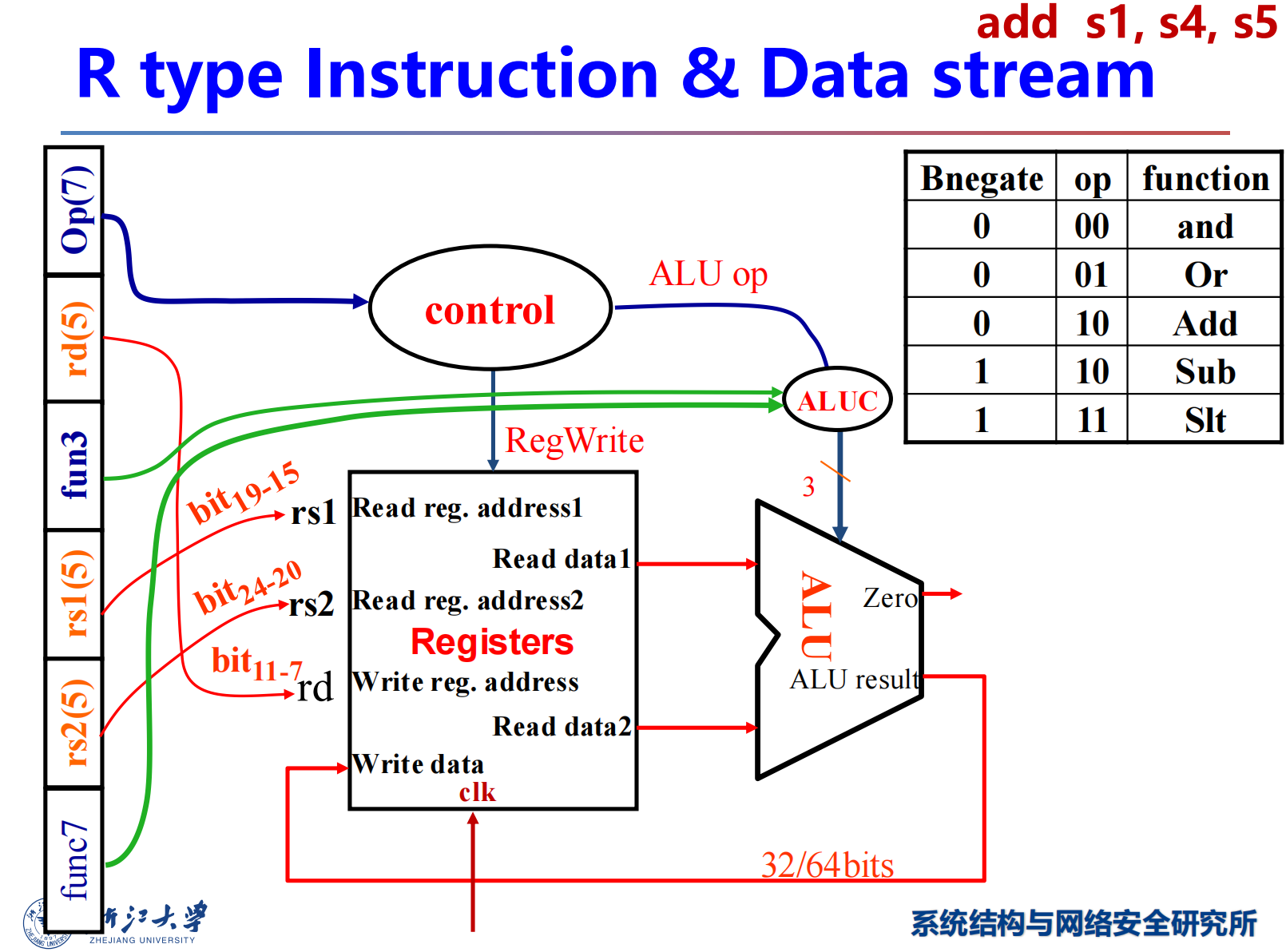

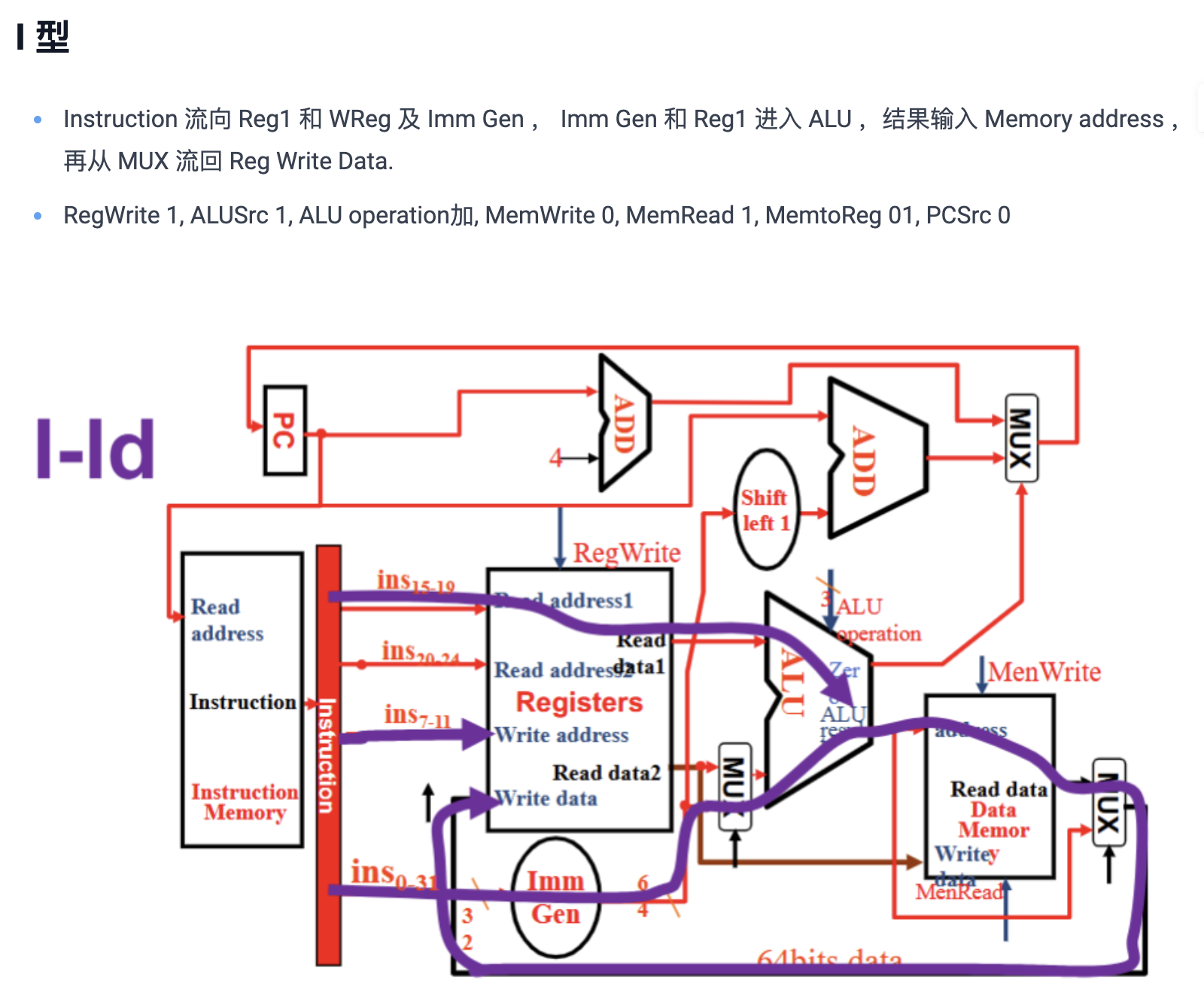

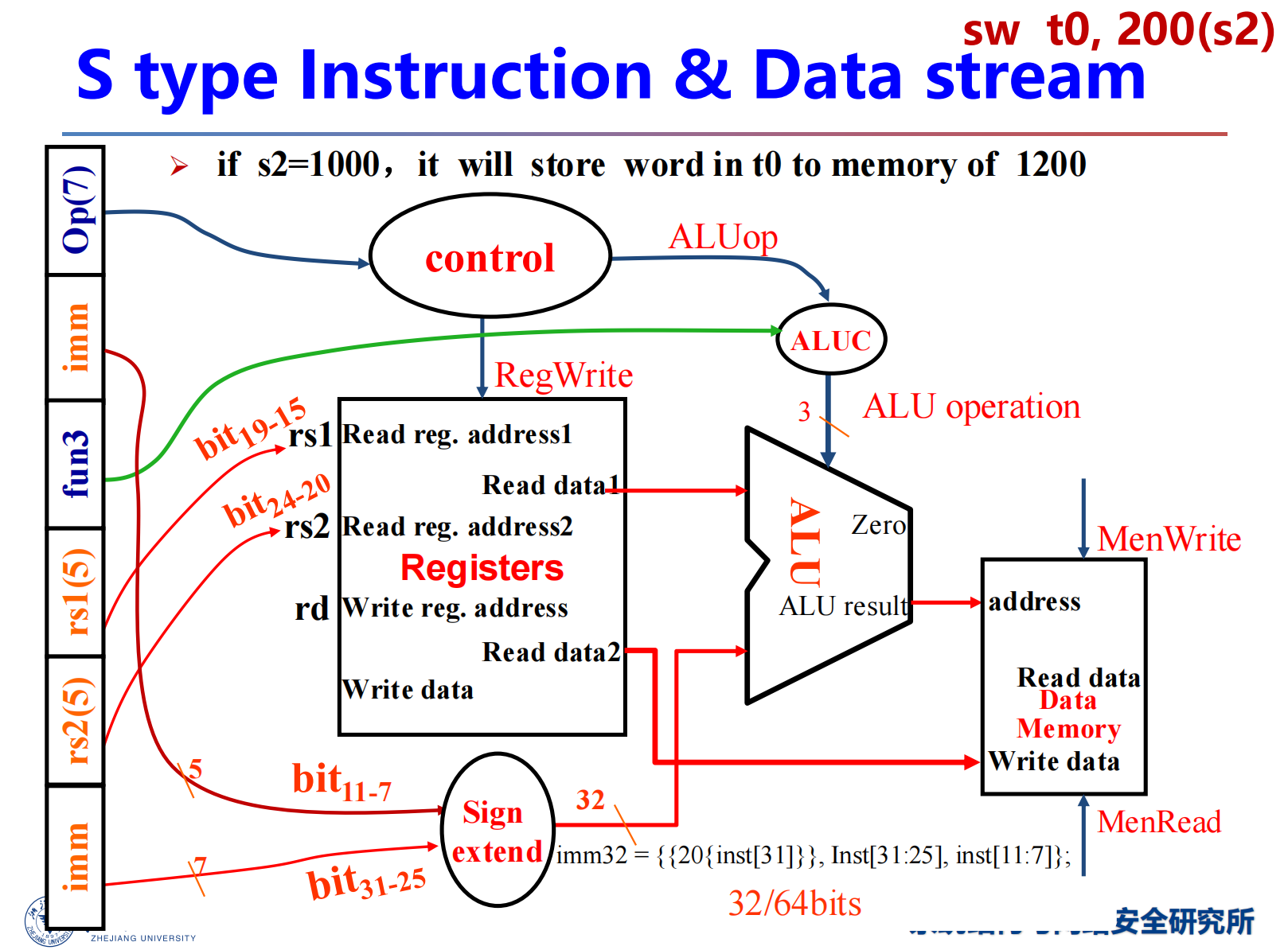

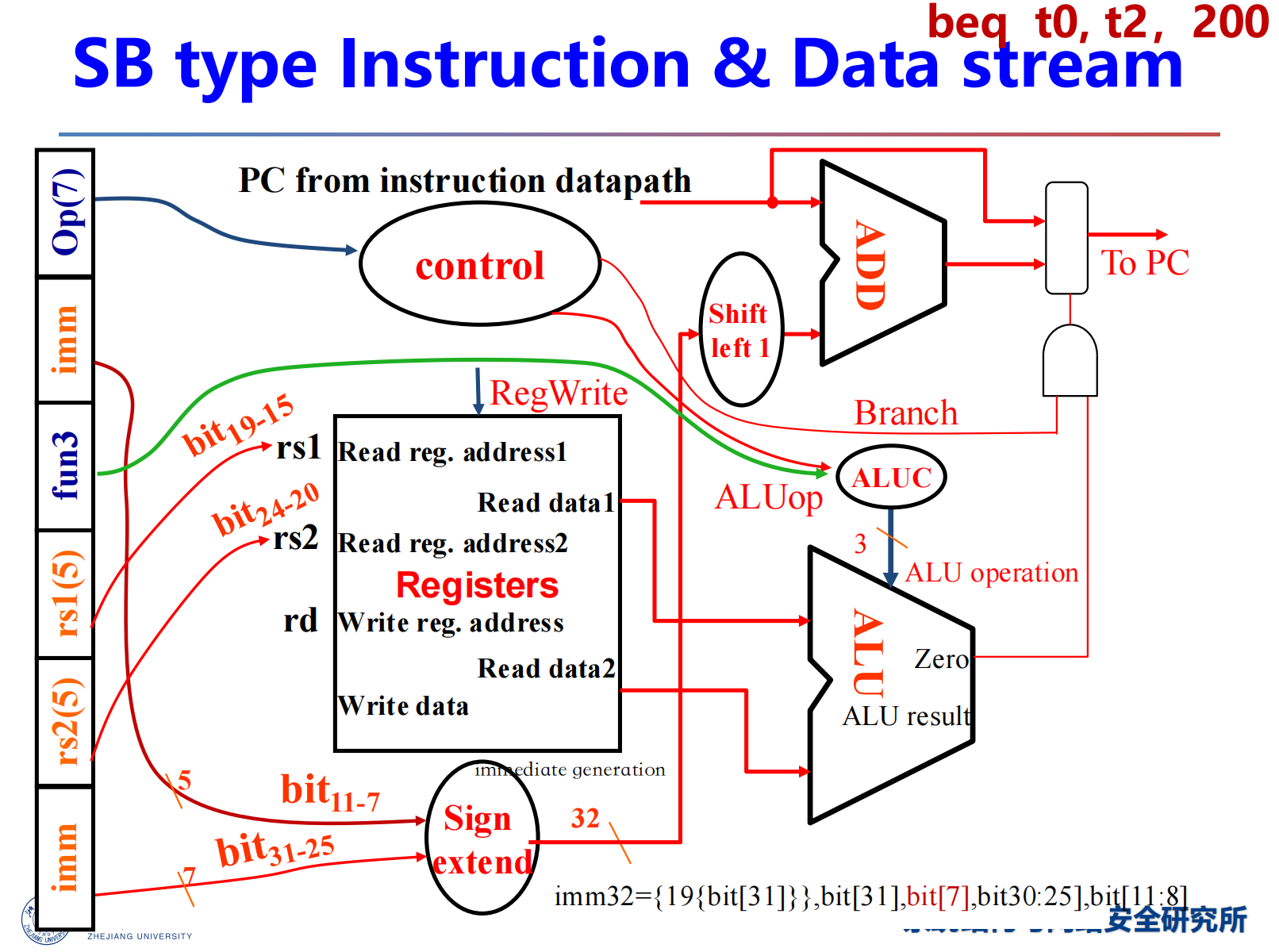

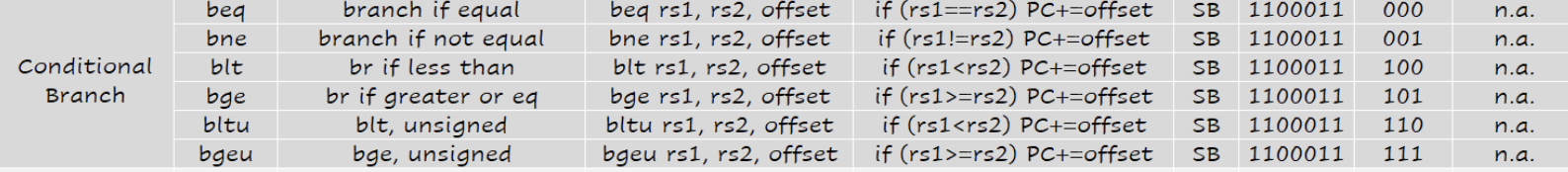

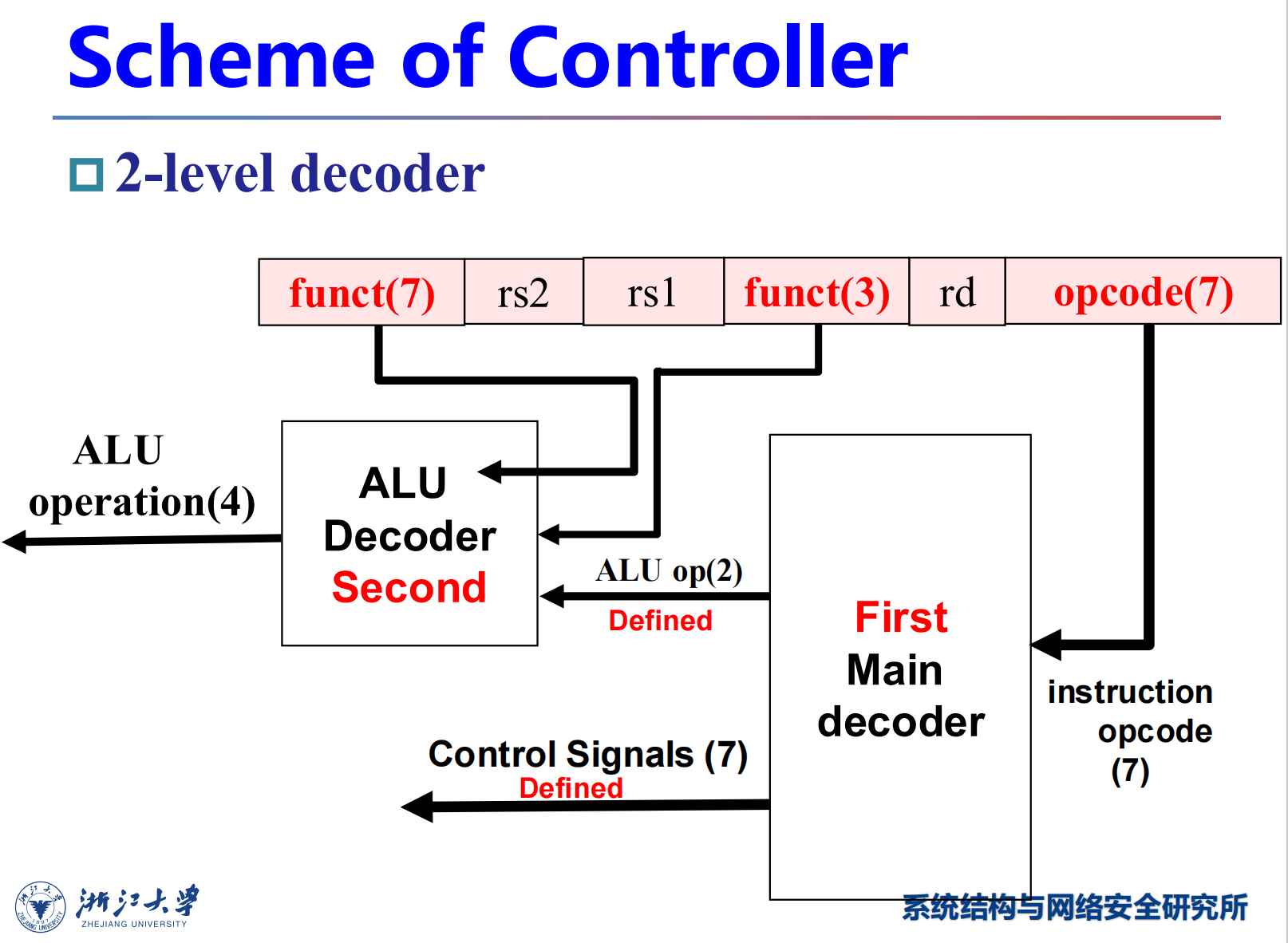

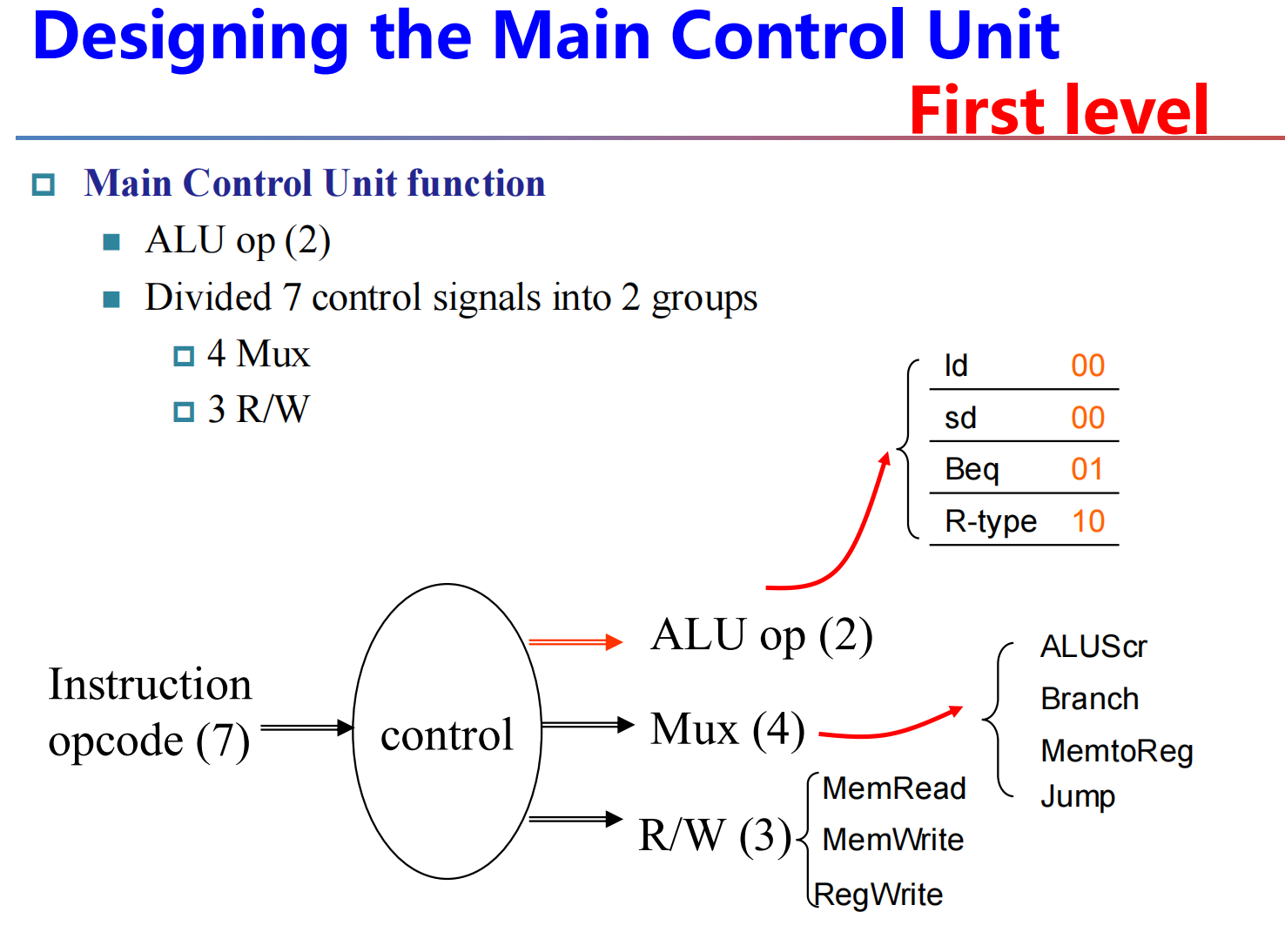

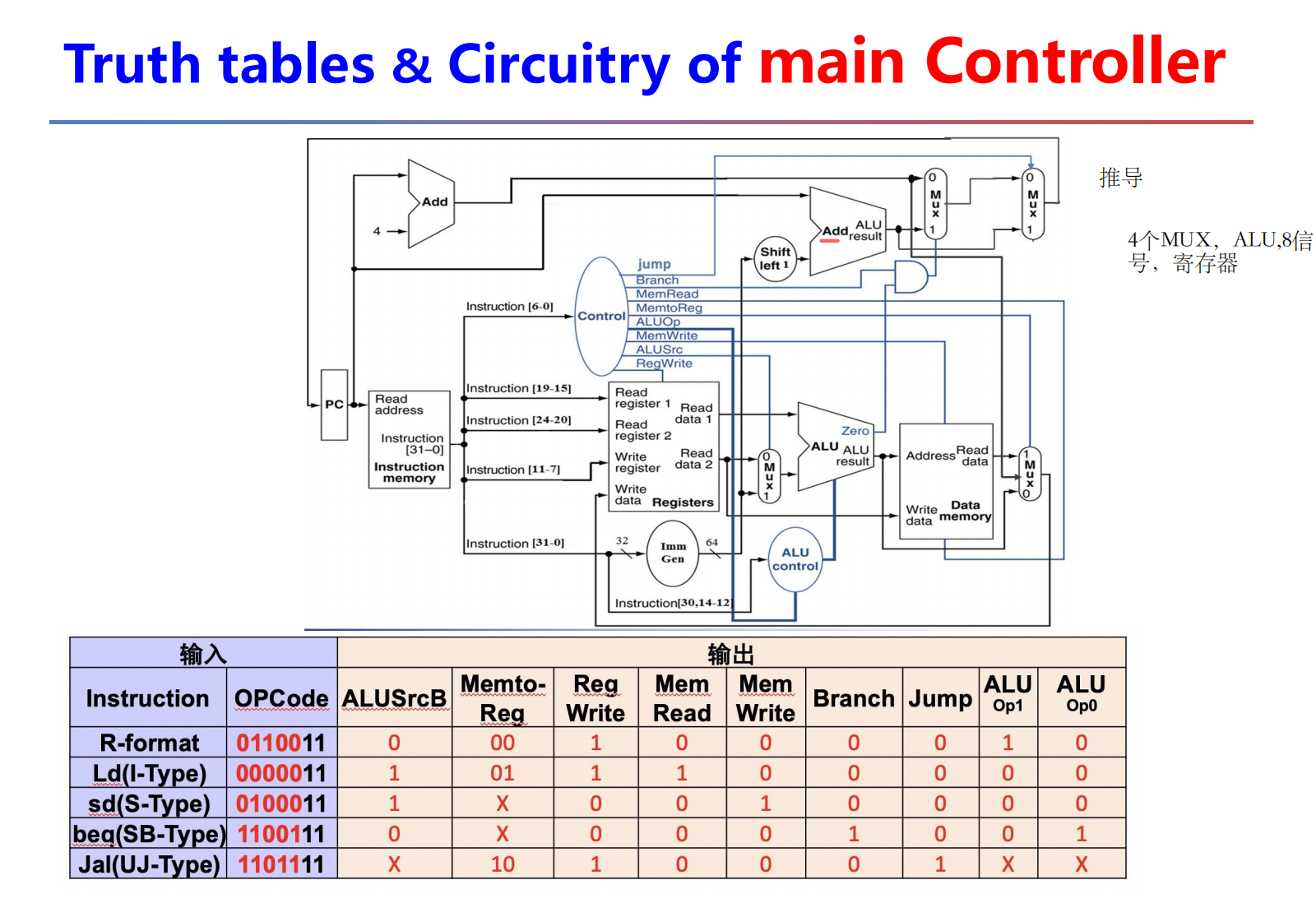

这一章Part1的核心就是搞懂不同类型指令执行在单周期CPU中的数据通路,重点关注controler(控制信号)&& MUX信号控制。

除此之外许多电路图需要记忆。

然后这一章节的笔记没有整理完,因此没有目录。

更新:期中考完了发现不同类型为什么对应不同的控制信号,整个数据通路怎么走怎么设计还是没有搞搞透。

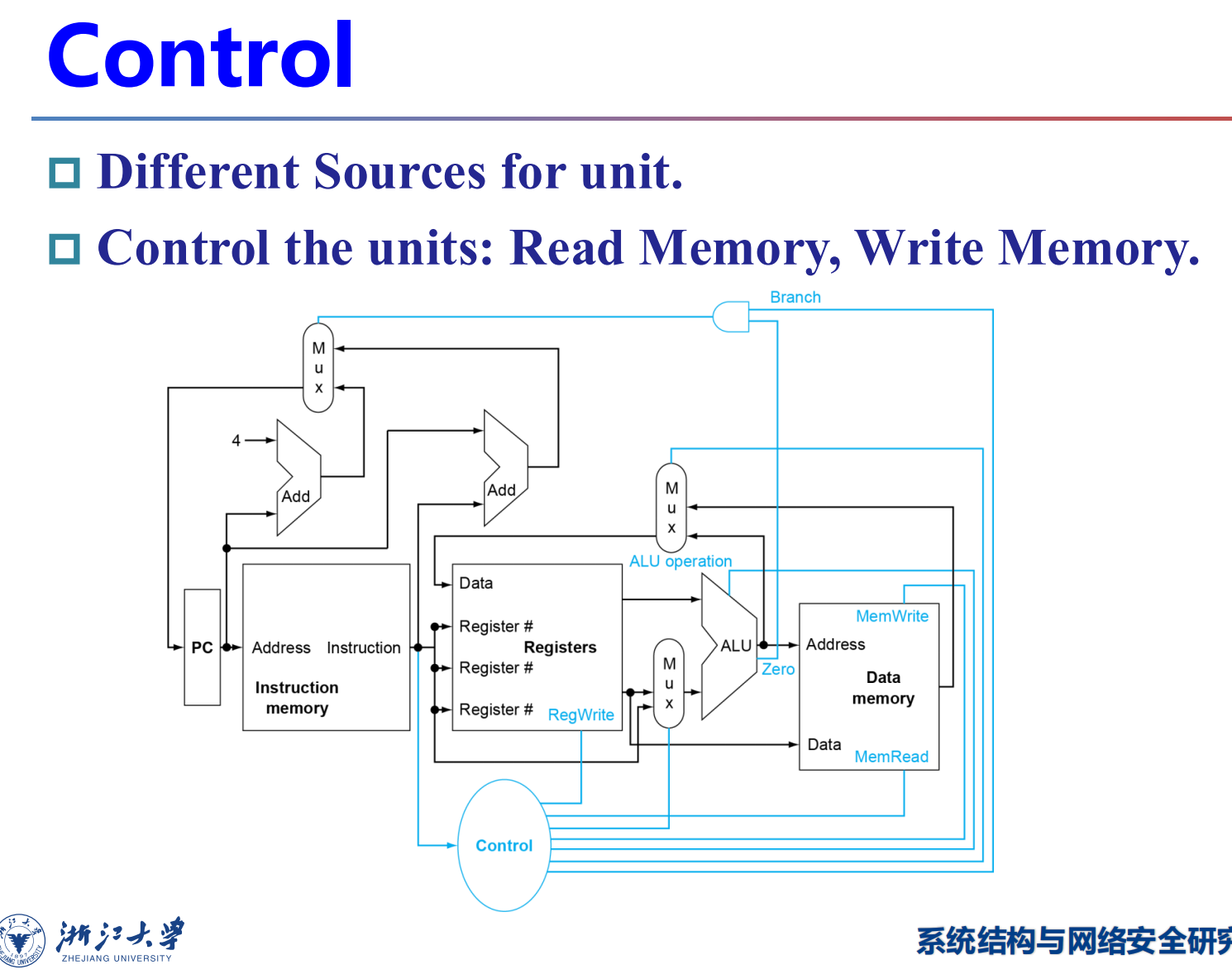

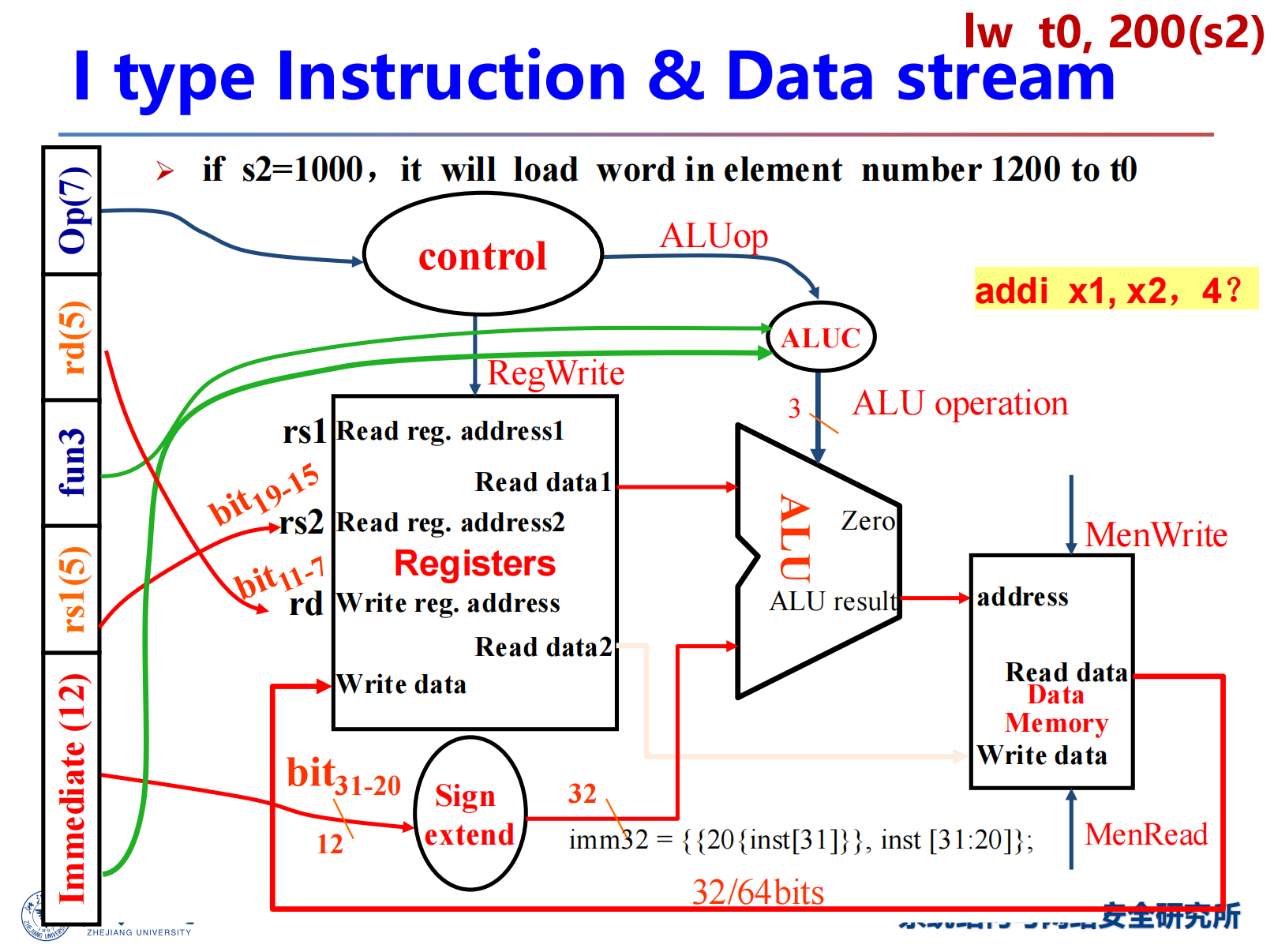

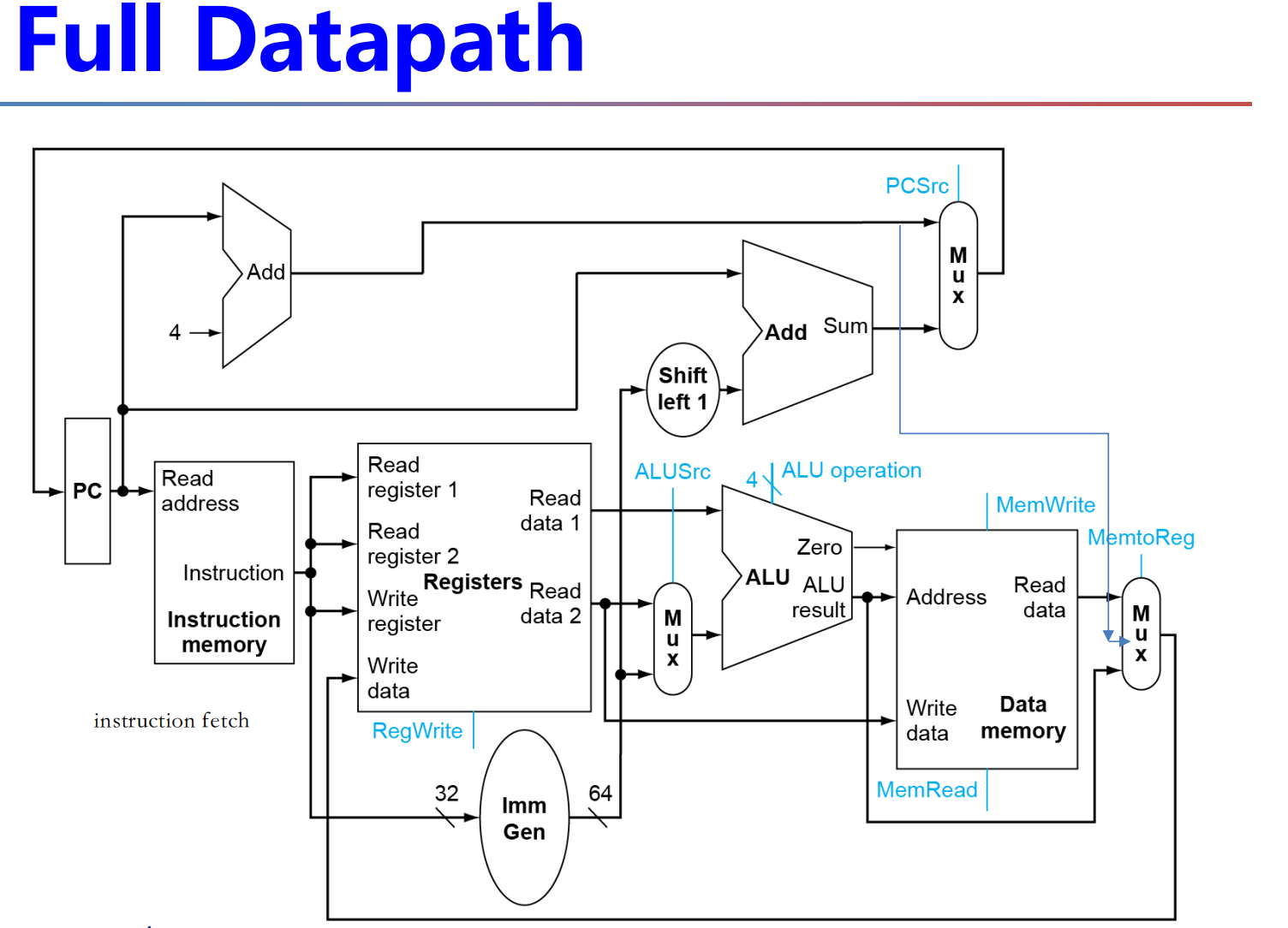

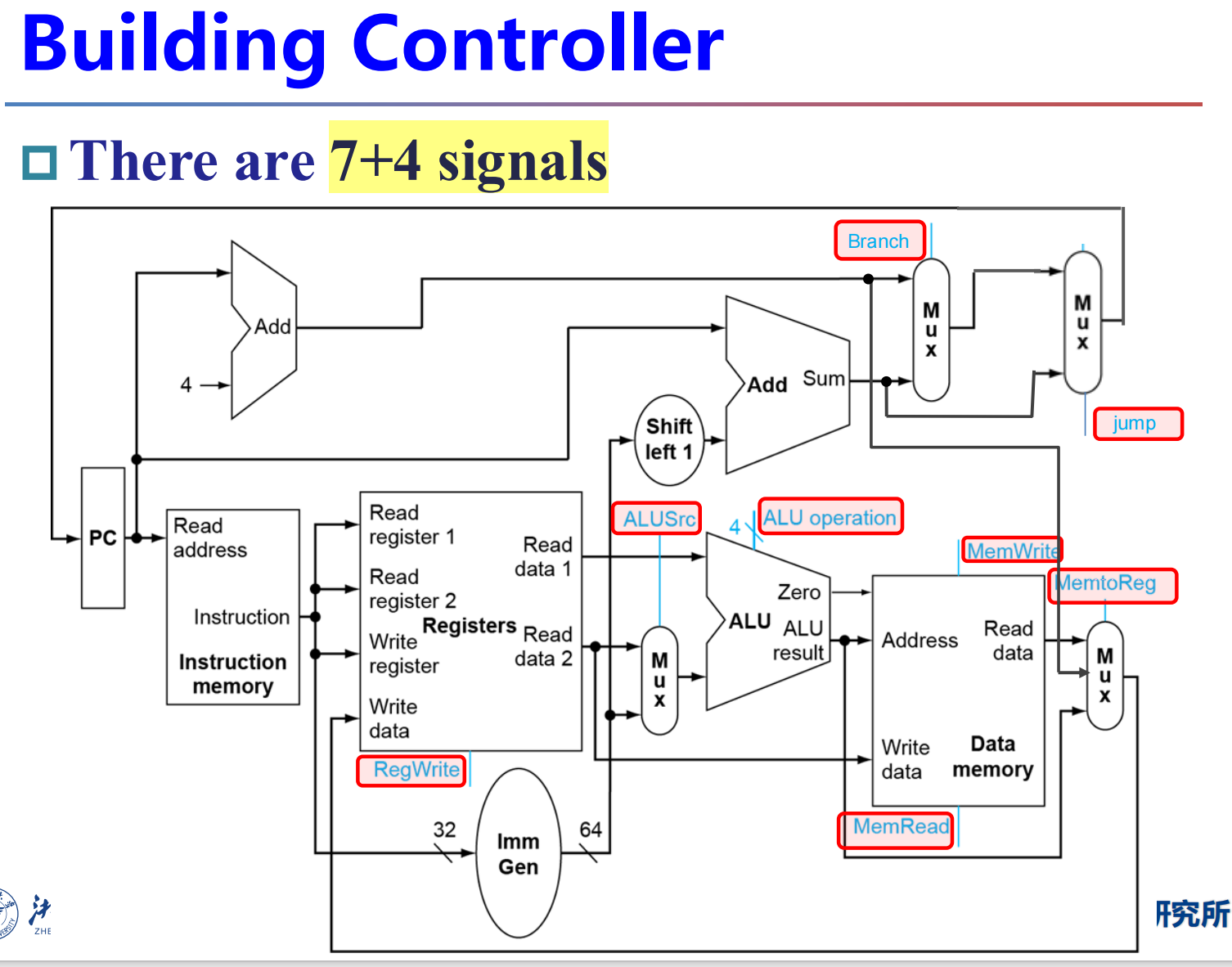

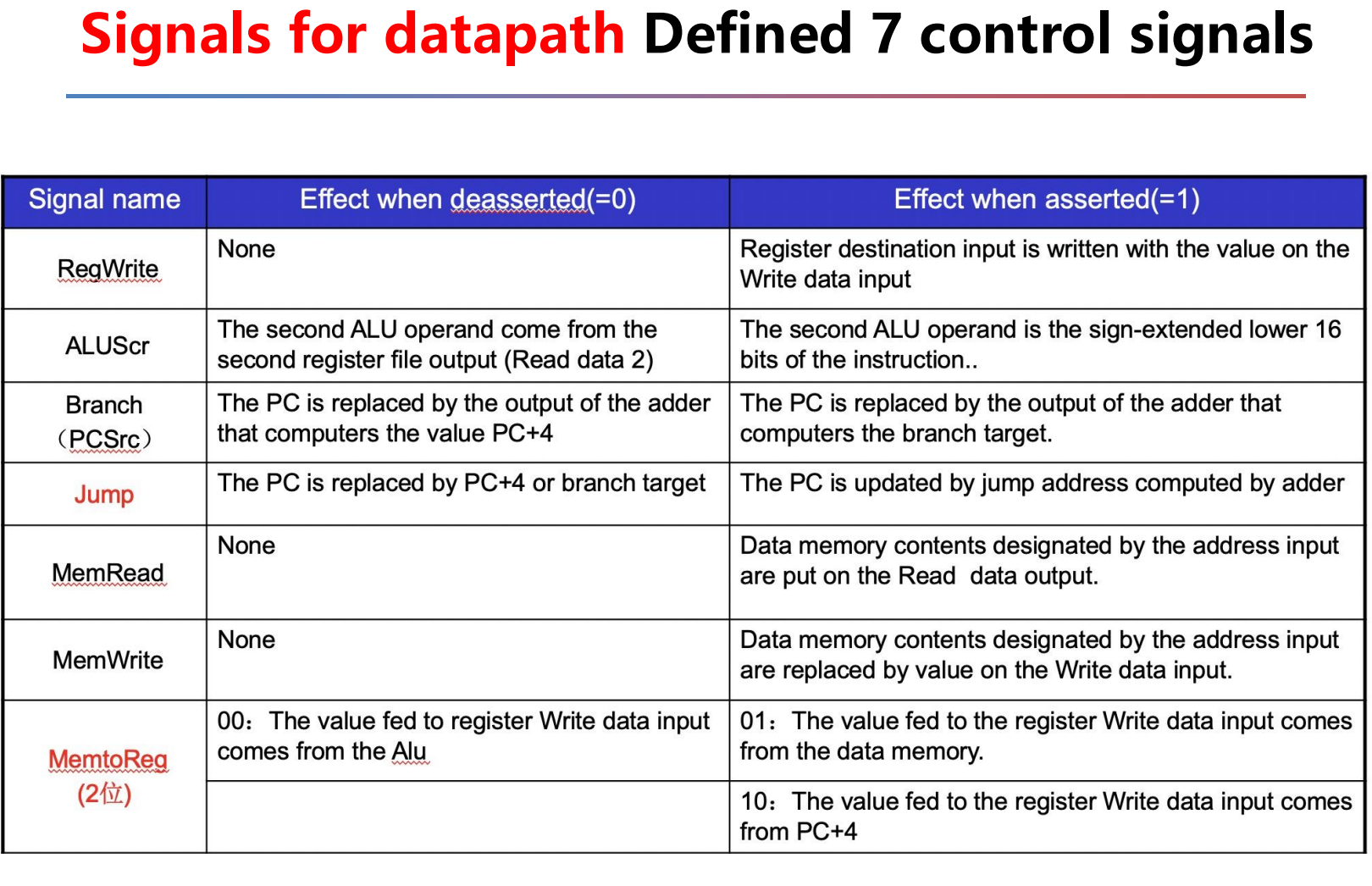

黑色代表data,蓝色代表control:  必须使用RegWrite和MemWrite作为使能,防止Registers和DataMemory错误写入 Q:为什么要加MemRead,寄存器不用加RegRead? A:因为memory读取很慢,能不读取时就不读取。(读取memory有风险,可能出现stop情况等待,延误时间)

必须使用RegWrite和MemWrite作为使能,防止Registers和DataMemory错误写入 Q:为什么要加MemRead,寄存器不用加RegRead? A:因为memory读取很慢,能不读取时就不读取。(读取memory有风险,可能出现stop情况等待,延误时间)

数据通路

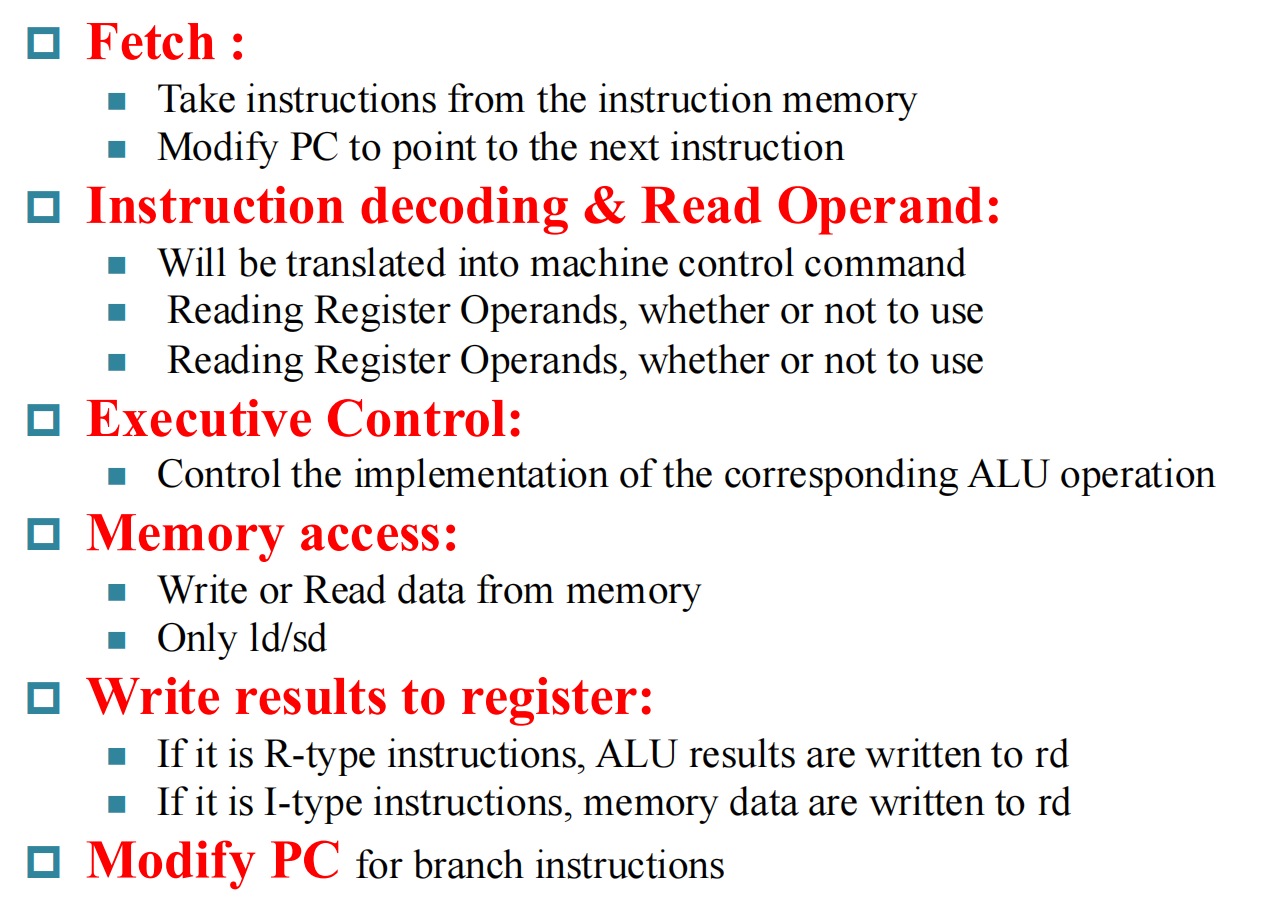

牢记前五个步骤: 希望前五个时间尽可能相近。 modify PC

希望前五个时间尽可能相近。 modify PC

Imm Gen 模块里有3:1MUX吗

“Load 指令和 Store 指令的数据通路操作留作习题。” ??

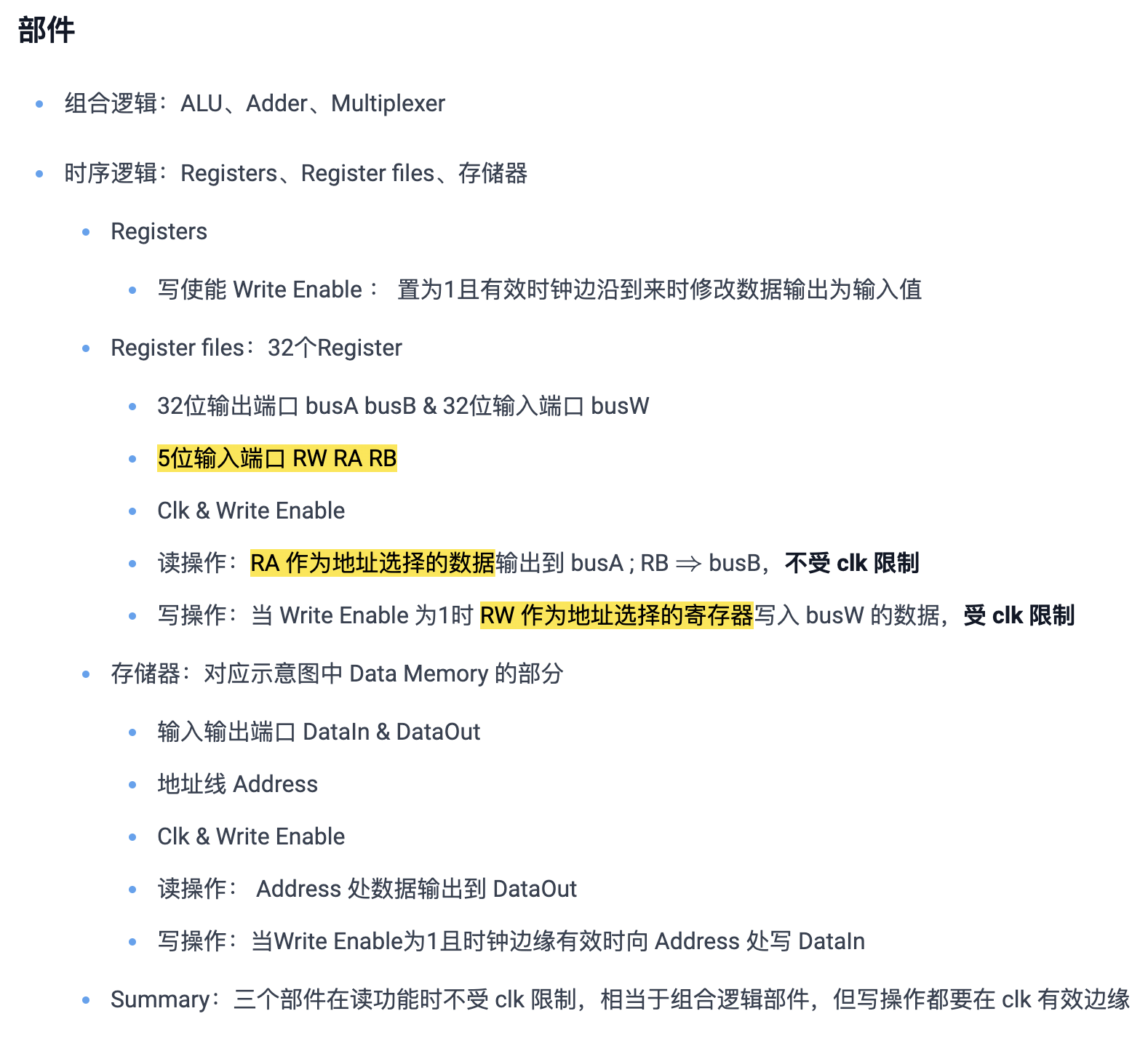

register和register file还是有区别的

Register files包含32个Register

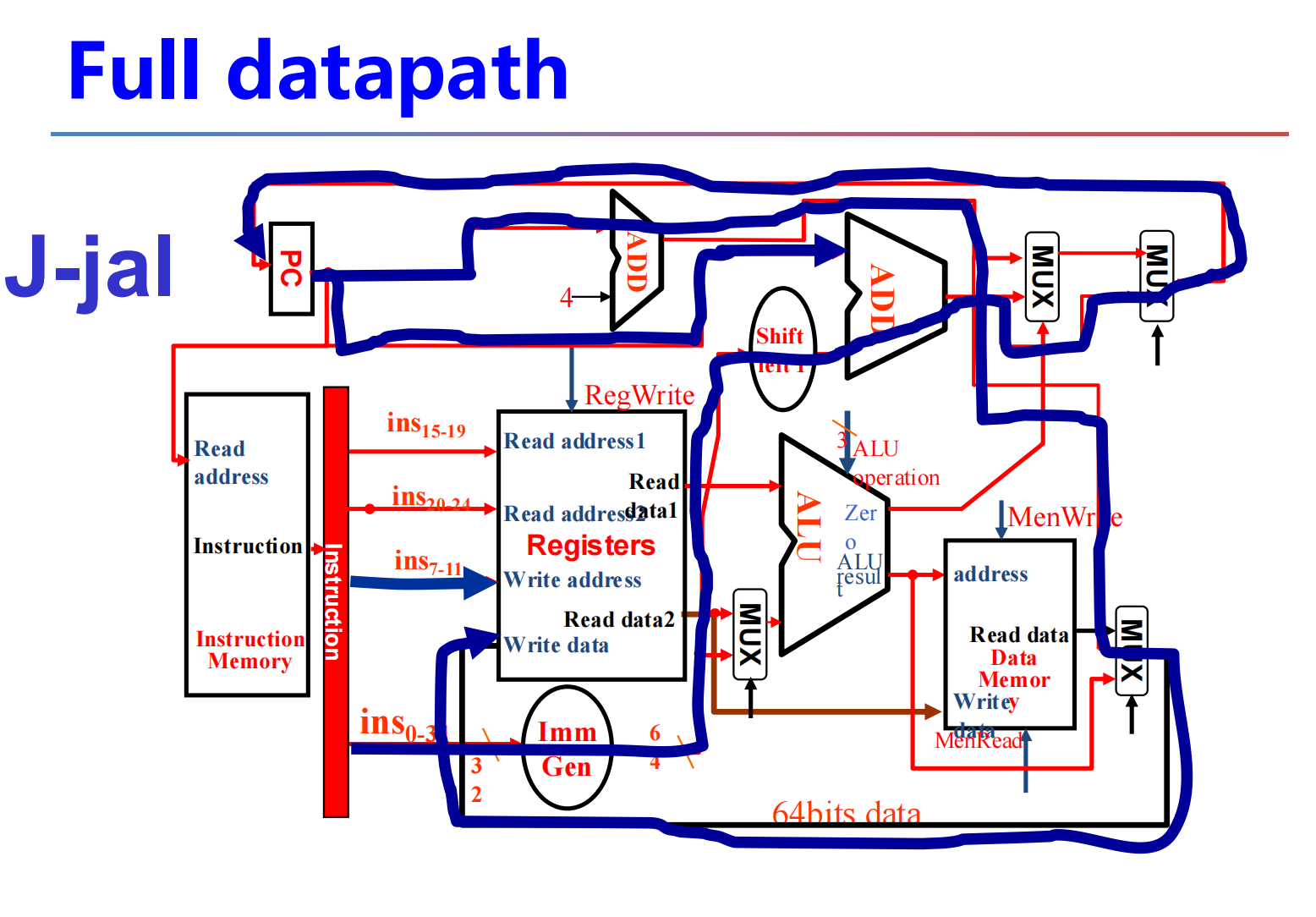

Datapath:这里JA笔记没看懂,没图。

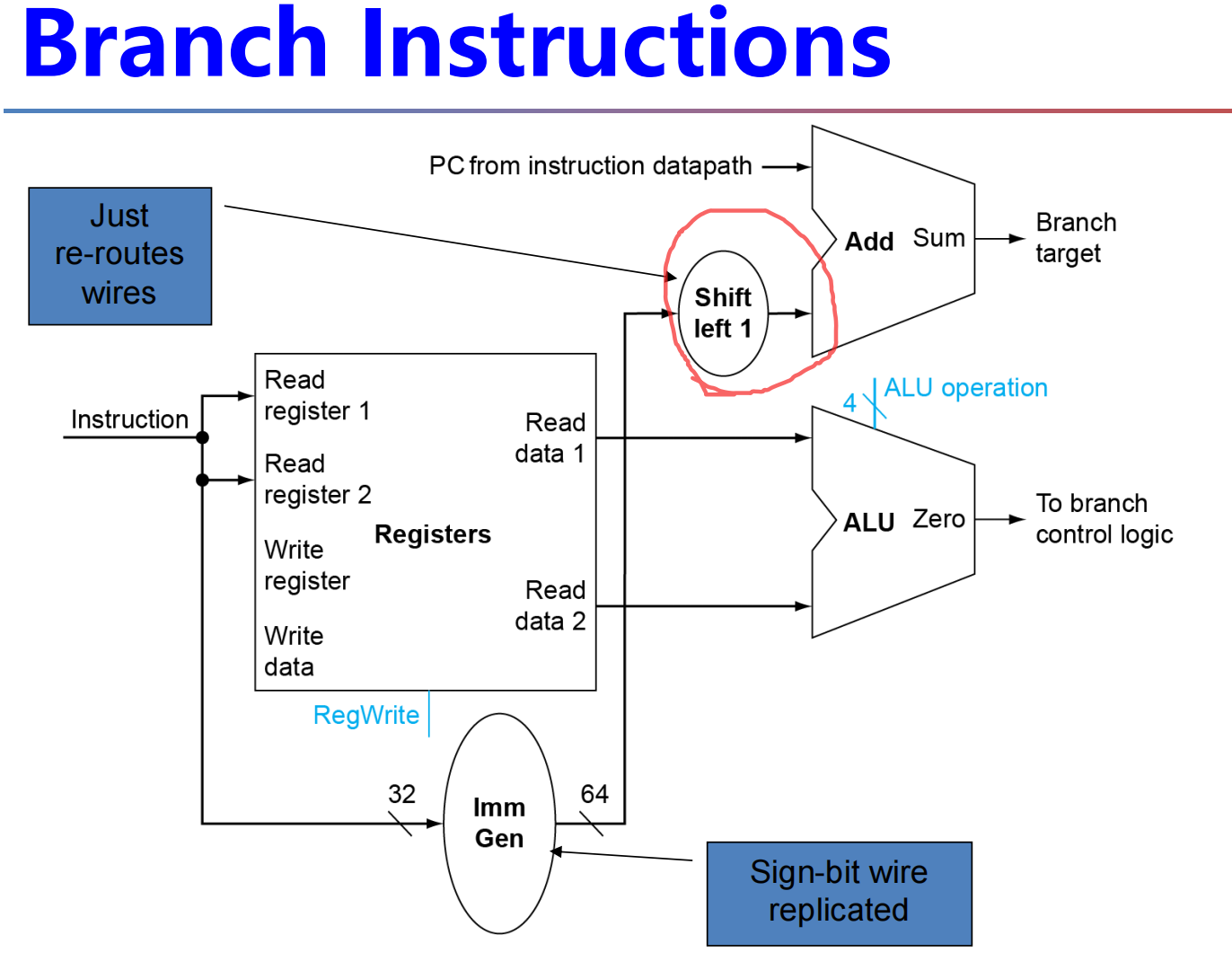

single-bit wire replication 符号位线复制

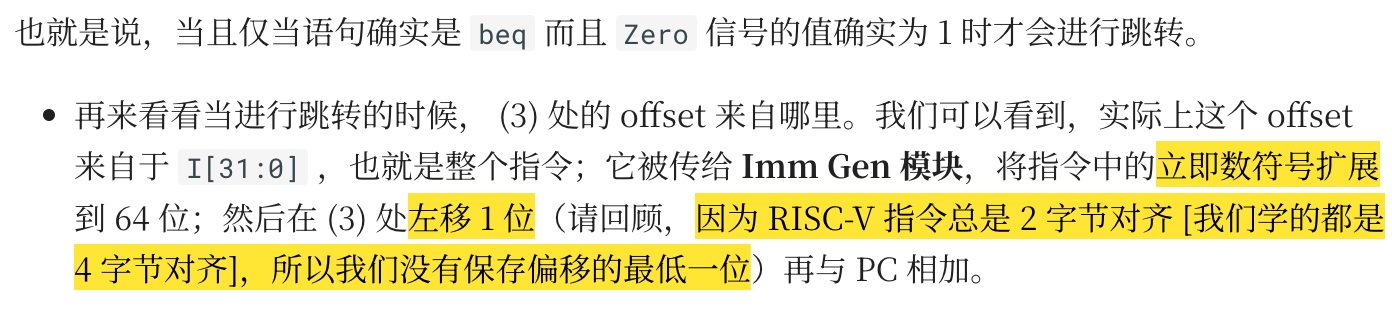

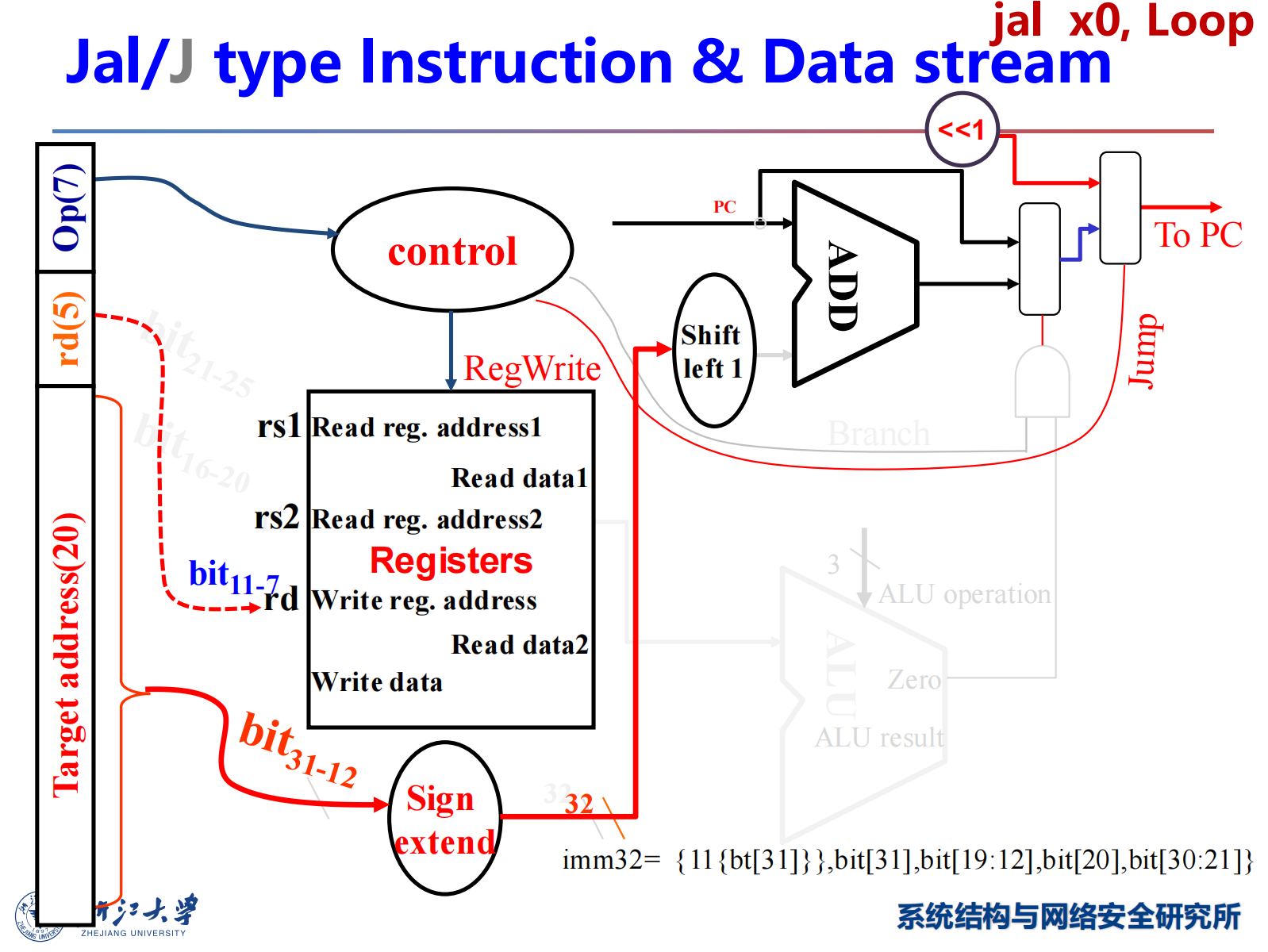

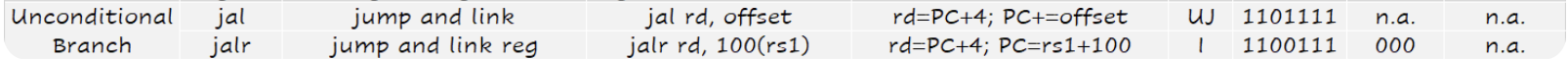

注意最右上角加了一个MUX,单独实现jal功能(jump信号) 为啥要<<1

【计组】第四章整理(Part 1)

https://tillyendless.github.io/posts/计组第四章整理part-1/